[TeledyneLeCroy] "SerDes (Serializer/Deserializer)" 포스팅 업데이트

- 2022-08-08

- 조회수2665

SerDes

직렬/병렬 변환기로,트랜스미터에서는 병렬 비트 열을 질렬화하여 전송하고, 리시버 측에서는 수신되는 비트 열을 다시 원래의 병렬 비트로 분원하는 송수신 기능의 한 블록입니다.

직렬화된 시리얼 데이터 출력에 비트의 동기 클럭 정보가 포함되어 전송되며, 리시버 측에서는 데이터로부터 클럭 정보를 복구하는 블록(CDR, Clock Data Recovery)이 포함됩니다.

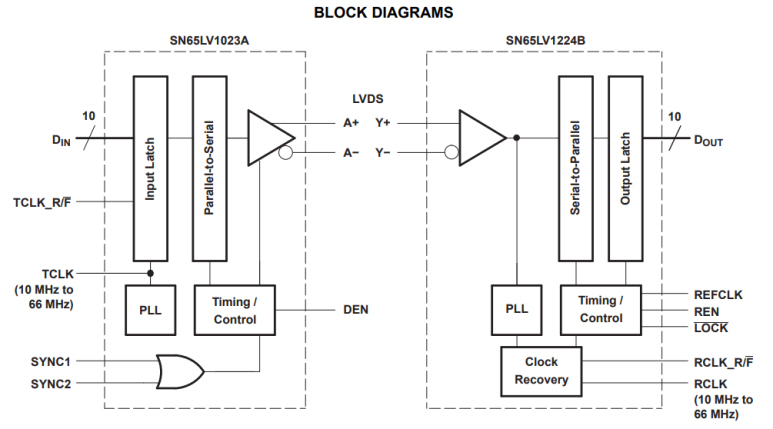

아래의 블록은 TI 사의 LVDS SerDes의 블록을 예로 보이고 있습니다.

그림 1. SerDes Block Diagram example (source : https://www.ti.com/)

적은 공간에서 많은 데이터를 전송할 수 있는 요구가 커지면서, 디지털 통신 버스는 병렬에서 시리얼 버스로 이동하고 있습니다. 데이터 스루풋은 높아지면서 소비 전력이 낮은 인터페이스들이 등장하고 이에 SerDes는 SATA, USB, PCI Express 등 일반적으로 사용하는 고속 인터페이스에서 거의 모두 사용하고 있습니다.

시리얼 버스의 장점 :

1) 클럭과 데이터의 스큐 문제 해결

2) 데이터 전송라인 현저히 적음.

병렬 인터페이스의 경우 버스의 폭이 넓어지면 넓어질 수록 많은 양의 버스 라인이 물리적으로 필요하며, 클럭과 각각의 데이터 레인 사이에서 발생하는 스큐 문제로 비트의 에러가 발생할 수 있습니다. 고속 시리얼 버스의 경우, 클럭 정보가 데이터 에지에 인코딩되어 전송되므로 병렬 인터페이스에서 발생하는 스큐로 인한 데이터 속도의 한계가 없습니다.

또한, 데이터 전송은 더 빠르게 하면서 시리얼화된 적은 수의 데이터 레인만 필요하므로 공간 적으로나 디자인 측면에서도 많은 장점이 있습니다.

시리얼화되면서 추가된 기술 :

전송 속도가 높아지면서 커넥터, 보드, 케이블등의 트랜스미터와 리시버 사이에 연결되는 물리적인 부품들의 제약으로 인해 ISI, Jitter, EMI 등의 문제가 발생할 수 있습니다. 물리적 제약을 넘어서기 위해 Pre-Emphasis, De-Empasis 및 SSC(Spread Spectrum Clocking)등의 추가적인 면들을 고려할 필요가 있습니다. 속도가 높아지고 시리얼화 되었다고 해서 반드시 신호의 무결성이 보장되는 것은 아니기 때문입니다.

또한 리시버 측면에서도 아날로그적인 이퀄라이저 및 디지털 방식의 이퀄라이저등의 기술이 요구됩니다.

분석장비 :

텔레다인르크로이에서는 SerDes를 포함하고 있는 트랜스미터와 리시버의 특성을 파악할 수 있는 측정장비로 SDA(Serial Data Analyzer)를 공급하고 있습니다. PCIe Gen4/Gen5/Gen6 를 비롯한 다양한 인터페이스의 컴플라이언스 테스트는 물론 디버깅 목적으로 사용할 수 있으며, 매우 자세하고 정밀한 측정 값을 제공하고 있습니다.