[TeledyneLeCroy]‘PCIe 링크의 들여다보기’ 주제의 포스팅 업데이트

- 2022-09-14

- 조회수2957

PCIe 링크 들여다보기

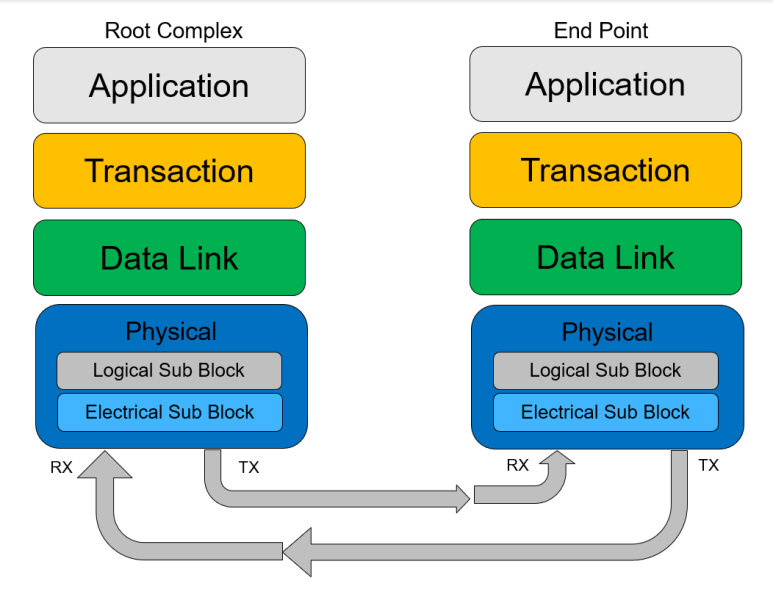

그림 1: 루트 컴플렉스와 엔드 포인트오의 PCIe Link. 각 디바이스에 자체적으로 트랜스미터와 리시버가 있습니다.

PCIe® (Peripheral Compnent Interconnect Express)는 다양한 컴퓨팅 및 통신 플랫폼에 적용할 수 있도록 설계된 고성능 범용 입/출력(I/) 상호 연결 인터페이스입니다. 는 다양한 컴퓨팅 및 통신 플랫폼을 위해 설계된 고성능 범용 입/출력(I/O) 상호 연결입니다. 최근 발표한 표준은 고속 시리얼 테크놀러지, 포인트-포인트, 스위치 기반 기술 및 패킷환된 프로토콜의 장점을 활요하고 있습니다. 루트 컴플렉스와 엔드 포인트는 링크 트레이닝과 링크 협상(Negotiation)이 매우 중요하므로 서로 연관되어 있는 링크의 동작을 포착하고 확인하는 작업이 PCIe 디바이스를 디버깅하는 데 필수적입니다. PCIe 엔지니어가 디버깅을 수행하는 작업은 쉽지 않은 일입니다. 왜 그렇게 어려울까요? 먼저 PCIe 아키텍쳐를 확인해보고 어떤 동작이 수행되는 지 알아보겠습니다.

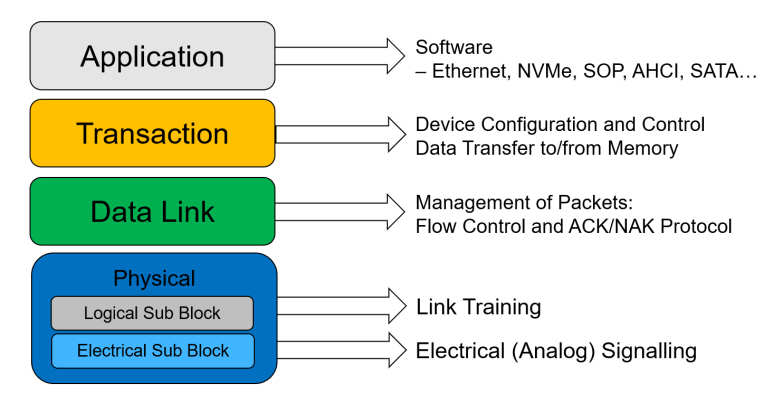

PCIe 아키텍처는 네트워크 통신의 일곱 계층 OSI 구조와 유사한 계층의 디자인을 가지고 있습니다(그림 2).

그림 2: PCIe 아키텍처는 Application, Transaction, Data Link, Physical Layer로 구성되어 있습니다.

Applicatin Layer(또는 호스트 레이어)는 사실 PCIe 사양에서 다루고 있는 범위를 벗어납니다. 이더넷, NVMe (Non-Volatile Memory Express) 및 기타 프로토콜과 같은 프로토콜이 페이로드 형태로 보이는 영역입니다. PCIe 프로토콜은 페이로드에 어떤 데이터가 포함되어 있는 지 상관하지 않고 링크를 통해 해당 데이터를 전송하는 방법을 정의하고 있습니다.

Transaction Layer는 링크의 디바이스들을 환경을 구성하는 데 사용됩니다. 호스트 메모리에서 디바이스로 또는 그 반대로 메모리를 전송하는 예를 생각해보십시오. 메모리 데이터를 읽기 또는 쓰기위한 명령이 있을 것이며, 기본적으로 디바이스 환경을 구성하고 열거해둔 다음 호스트에서 디바이스로 또는 디바이스에서 호스트로 데이터를 전송합니다. 이 부분에서 메시지 및 에러를 알리는 메커니즘도 가지고 있습니다.

디바이스와 디바이스 사이의 데이터 전송은 Data Link Layer에서 관리됩니다. 링크를 통해 전송되는 패킷의 무결성을 보장하기위한 흐름 제어 메커니즘과 Ack 프로토콜이 존재하는 레이어입니다. Data Link Layer는 또한 Physical Layer에게 "전력을 절약하기위해 절전 모드로 진입하겠다"라고 알리는 저전력 상태로의 진입을 관리합니다.

가장 낮은 레벨의 Physical Layer는 전기적 블록과 논리적 블록의 두개의 하위 블록으로 나뉩니다. 전기적 블록은 모든 아날로그 시그널링에 필요한 아날로그 부품들로 이루어져있습니다. 논리 블록은 링크 설정을 위해 State Machine을 사용하여 두 디바이스가 실제로 서로 데이터를 주고 받는 방법을 제어합니다. 링크 트레이닝 과정에서 다른 디바이스와 교환하는 트레이닝 시퀀스를 포함한 데이터 패턴을 생성합니다.

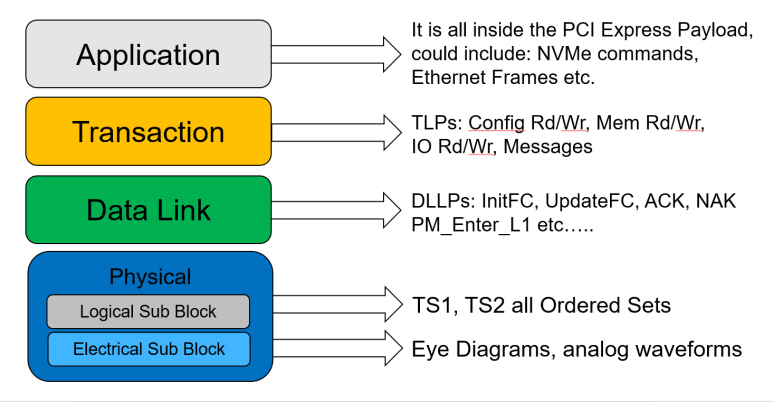

그림 3: PCIe 동작에서의 각 레이어별 트랜젝션

그림 3에서는 일반적으로 각 계층에서 볼 수 있는 메시지와 명령을 보이고 있습니다.

두 PCIe 디바이스가 서로 통신하면, 그것을 링크로 간주합니다. 각각의 디바이스들은 그림 1에서 보인 것과 같이 트랜스미터(TX)와 리시버(RX)를 각각 가지고 있습니다.

루크 컴플렉스/호스트를 엔드포인트에 연결하면 Application Layer 소프트웨어는 연결된 PCIe 링크를 사용하여 자기 자신과 엔드포인트 간에 데이터를 전송하려고 할 것입니다. 위에서부터 애플리케이션 소프트웨어를 인식하는 디바이스 드라이버는 PCIe 트래픽을 생성하여 Transaction Layer를 통해 Data Link Layer로 전달하고 Physical Layer로 전달하며 반대쪽 링크에도 전달합니다.

레이어가 하나 이상의 상위 레이어 또는 하위 레이어 동작에 상관하지 않기때문에 문제가 발생할 수 있습니다. 예를 들어 Data Link Layer의 흐름 제어 또는 에러 수정작업은 Application Layer와는 무관하지만, 성능에 영향을 미칠 수 있습니다.

디버깅 작업에서 발생할 수 있는 다른 문제는 서로 다른 계층들의 트랜젝션에 접근하려면 서로 다른 테스트 장비가 사용된다는 것입니다. 오실로스코프는 물리계층의 전기적 신호와 하위 레벨의 논리적 동작을 포착하여 확인하는 데 사용됩니다. 프로토콜 분석기는 모든 상위 레벨의 논리적 동작을 기록하고 표시하는 장비입니다. 오실로스코프의 경우 수 밀리초 시간을 포착할 수 있으며, 프로토콜 분석기의 경우 수 분의 이벤트를 포착할 수 있으며, 확인할 수 있는 이벤트 길이가 다릅니다. 또한 오실로스코프에서는 아이다이어그램, 파형, 아난로그 신호의 정보를 확인하거나 하위 논리 블록 데이터를 디코딩하여 보여 줄 수 있습니다. 포로토콜 분석기는 시리얼 데이터 패킷에 대한 자세한 정보를 제공하며, 패킷의 일부 심볼이나 비트 단위의 디코딩을 수행할 수 있습니다. 완벽하게 시간을 일치시킬 수 있는 방법이 있다고 하더라도 서로 다른 두 장비에서 포착된 데이터가 서로 어떻게 연관되어 있는 지는 즉시 알아볼 수 없습니다.

PCIe 링크의 전체 동작을 확인하는 유일한 방법은 오실로스코프와 프로토콜 분석기의 동작을 연결하는 것입니다. 이것이 PCIe CrossSncTM PHY가 정확하게 수행하는 작업입니다. 사용에 대한 구체적인 방법은 다음 포스팅에서 설명드리겠습니다.