[TeledyneLeCroy]‘L1 하위 상태 타이밍에러 CrossSync PHY로 디버깅’ 주제의 포스팅 업데이트

- 2022-09-19

- 조회수3036

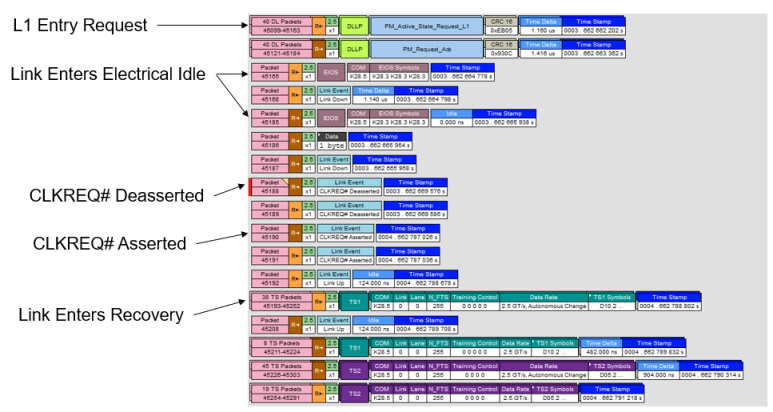

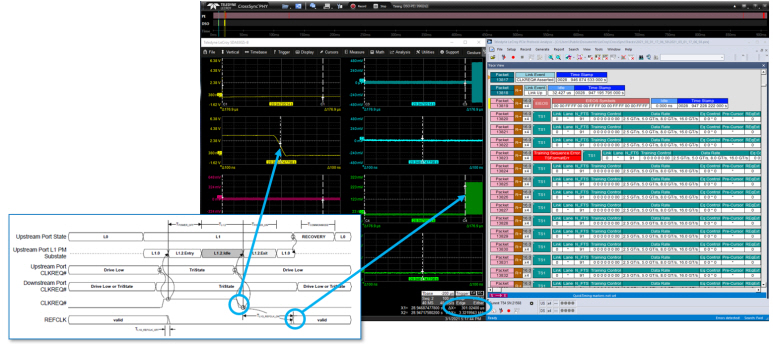

그림 1: PCIe용 CrossSync PHY를 사용하면 L1 하위 상태 이벤트의 프로토콜 계층와 전기적 신호를 쉽게 매핑할 수 있습니다.

PCIe® 전원 관리에 사용되는 L1 Substate를 디버깅하는 것은 엔지니어, 특히 M.2 폼 팩터를 사용하는 엔지니어에게 사실 쉽지 않은 일이었습니다. L1.1 및 L1.2 서브스테이트를 사용하면 PCIe 링크를 L1 상태에 있는 것 보다 더 낮은 절전 상태로 전환할 수 있습니다. ASPM 메시지 또는 PCIPM 메시지의 두 가지 메커니즘 중 하나를 통해서만 L1 상태로 진입하지만, 두 가지 경우 모두 전기적으로 유휴상태가 됩니다. L1 상태를 유지하고 있는 것과는 다르게 CLKREQ# 신호를 사용하여 L1의 하위 상태(Substate)모드에 진입하거나 하위모드에서 빠져나올 수 있습니다. L1 하위 상태에 진입하면, 디바이스 또는 호스트는 CLKREQ#은 deassert 즉 신호를 보내지 않음으로써, "더 이상 클럭이 필요없습니다." 라고 상대방에게 알려줌으로써 클럭 발생을 멈추면서 추가적으로 전력을 절약할 수 있습니다. L1 하위 상태에서 나올 때는 CLKREQ#이 설정 즉, 신호를 보내면서 기준 클럭 생성이 다시 시작됩니다.

그림 2: CLKREQ#이 설정되었다가 다시 deassert되었다가 assert 되는 동안 발생하는 동작 - 프로토콜 분석기 단독으로는 볼 수 없는 동작

프로토콜 분석기에서는 이런 하위 상태가 클럭요청(CLKREQ#)라인이 토글되었다는 정보외에 실제로 어떤 모습으로 동작했는 지는 확인할 수 없습니다. 그림 2에서는 프로토콜 분석기의 트레이스를 보이고 있으며, 맨위의 라인에서는 L1 하위 상태모드에 있는 레인에 L1에 다시 진입하라는 요청이 디코드되었으며, 전력관리 요청에 응답한 후 링크가 유휴상태(Electrical IDLE)로 가기 직전의 상태인 EIOS가 전송되었고 그 후에 클럭 요청 라인이 deassert되었다는 것을 알 수 있습니다. 하지만 이 시간동안 클럭 요청라인에서 전기적인 관점에서볼 때 어떤 이벤트들이 있었을까요? 프로토콜 분석기에서는 전기적으로 어떤 일이 발생했는지는 알 수 없습니다. 이런 상태를 확인하기위해서는 오실로스코프가 필요합니다. CLKREQ#가 assert 되면서 기준 클럭이 출력되는 시점까지의 타이밍에 문제가 발생한 경우 프로토콜 분석기에서는 확인할 수 없습니다. 이런 문제를 디버깅할 때 PCIe CrossSyncTM PHY를 적용하면 쉽게 디버깅할 수 있습니다.

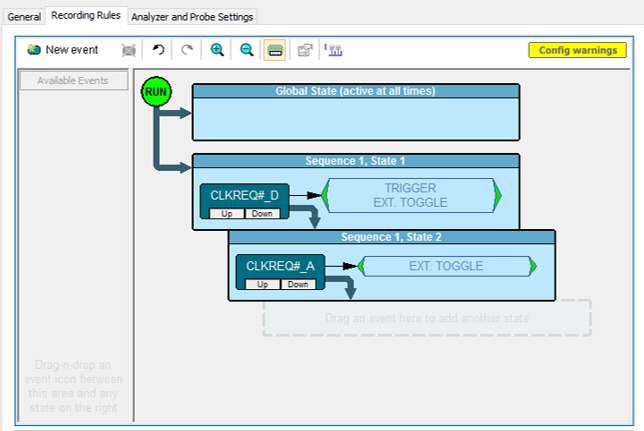

그림 3: CLKREQ#와 같은 프로토콜 이벤트가 발생했을 때 파형 또는 데이터를 포착하도록 설정한 예

CrossSync PHY 테크놀러지는 프로토콜 분석기를 사용하여 CLKREQ#와 같은 상위 레벨의 프로토콜 이벤트가 발생되었을 때 오실로스코프를 트리거 할 수 있습니다. 프로토콜 분석기와 오실로스코프가 데이터 수집을 시작하는 L1 상태에서 CLKREQ#이 deassert 될 때 오실로스코프를 트리거할 수 있도록 프로토콜 분석기의 레코딩 옵션을 설정합니다. 오실로스코프의 시퀀스 모드를 사용하면 유휴 시간(IDLE Time) 동안의 이벤트는 저장하지 않을 수 있어 메모리를 낭비를 막을 수 있을 뿐만아니라 관심 있는 시간에만 기준 클록 신호의 두 오실로스코프 수집을 수행할 수 있습니다.

프로토콜 분석기와 오실로스코프가 동시에 트리거되어 시간적으로 동기화된 데이터를 나란히 두고 검색하면 기준 클럭 신호에서 동시에 트리거된 시간 동기화 수집을 나란히 탐색하면 실제로 L1 하위 상태로 진입했다 나오는 순간을 기준 클럭 신호에서 확인할 수 있습니다. CrossSync 윈도우내에서 오실로스코프 파형 또는 프로토콜 분석기의 패킷을 클릭하면 두개의 화면에 같은 시점으로 이동합니다. 윈도우 안에서 오실로스코프 채널 또는 프로토콜 분석기 패킷 디스플레이를 클릭하면 두 디스플레이가 동일한 시점으로 이동합니다. 또한 탐색 표시줄을 사용하여 두 수집에서 동시에 다른 시간 창을 확대할 수도 있습니다.

커서와 측정 파라미터와 같은 모든 일반적인 오실로스코프 측정 툴을 이용하여 기준 클럭과 데이터 링크 이베트 사이의 시간차를 측정할 수 있습니다. 오실로스코프에서 포착한 파형에서 기준 클럭이 시작된 시점에 시간 커서를 위치 시킨 후 CLKREQ# assert 이벤트와의 시간차를 측정합니다(그림 1). 오실로스코프 획득에서 유효한 기준 클럭의 시작을 식별한 후 수평 커서를 거기에 놓고 다음의 델타를 측정합니다. 유효한 기준 클럭에 대한 CLKREQ# 어설션(TL10_REFCLK_ON); TS1 패킷에 대한 유효한 참조 클럭; SDS 패킷에 대한 유효한 참조 클럭(L0의 시작). 기준 클럭이 실제로 유휴 상태에 진입했다가 다시 활성화되는 시점을 데이터 링크 계층에서 동시에 발생한 이벤트들과 비교하면 진입했다 벗어나는 시점이 사양 및 디자인한 범위내에서 동작하고 있는지 확인할 수 있습니다.